1비트 4to1 mux의 출력 데이터 유형: wire 및 reg

다중 코드는 다음과 같이 작성하는데 아래 코드는 회로 합성 오류를 발생시킨다. 컴파일 후 합성된 회로를 보고 오류가 있는 부분을 수정합니다. 문제가 표시되었습니다. 이것을 해결합시다.

module mux4x1 (sel,d0,di,d2,d3,m1,m2);

input (1:0) sel;

input d0,dl,d2,d3;

output m1, m2;

wire ml;

reg m2;

assign ml = sel(i) ? (sel(0)? d3 : d2)

: (sel(0)? d1 : d0)

always @ *

if (sel==2'b11) m2 = d3;

else if (sel==2'b10) m2 = d2;

else if (sel==2'b01) m2 = dl;

else if (sel==2'b00) m2 = dO;

endmodule

이것은 Xilinx Vivado 인코딩입니다.

module mux4x1 (sel, d0, d1, d2, d3, m1, m2);

input (1:0) sel;

input d0,d1,d2,d3;

output m1, m2;

wire m1;

reg m2;

//MSB이므로 D2나D3 선택

assign m1 = (sel(1))?(sel(0)? d3:d2) : (sel(0) ? d1 : d0);

always @ (sel,d0,d1,d2,d3)

begin

if(sel==2'h3) m2 = d3; // 하고싶은걸로 하면된다.

else if(sel==2'h2) m2 = d2;

else if(sel==2'h1) m2 = d1;

else m2 = d0;

end

endmodule

오류의 원인은 변수 값이 거의 항상 지정되지 않았기 때문이라고 가정합니다.

위 코드와 다른 점은 Else If 대신 Else 문을 사용한다는 것입니다.

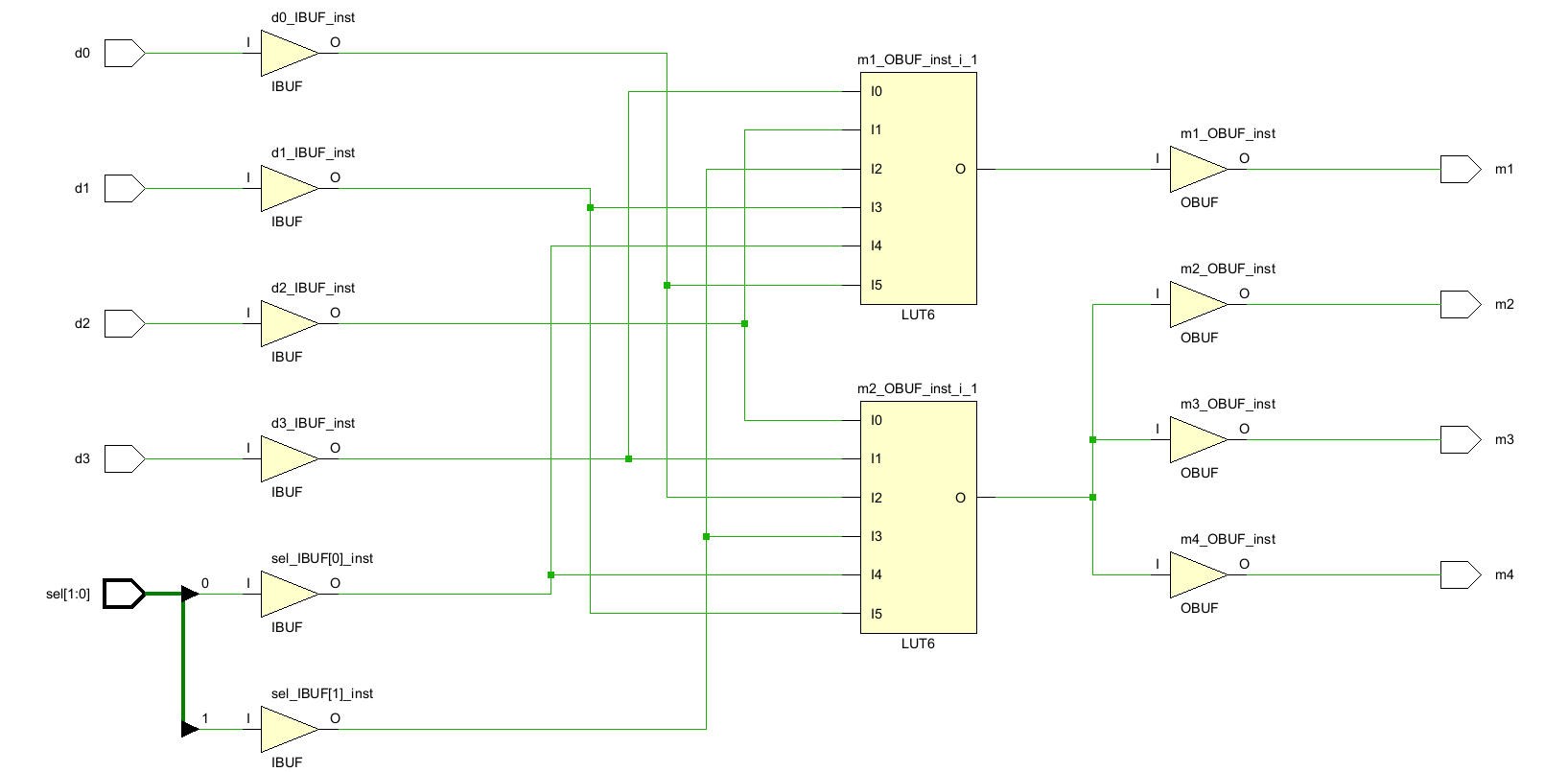

SYNTHESIS의 스키마를 보면 정상적으로 설계되었음을 알 수 있습니다.